# ACTA

# UNIVERSITATIS OULUENSIS

Kimmo Lasanen

INTEGRATED ANALOGUE CMOS CIRCUITS AND STRUCTURES FOR HEART RATE DETECTORS AND OTHER LOW-VOLTAGE, LOW-POWER APPLICATIONS

UNIVERSITY OF OULU, FACULTY OF TECHNOLOGY, DEPARTMENT OF ELECTRICAL AND INFORMATION ENGINEERING; UNIVERSITY OF OULU, INFOTECH OULU

## ACTA UNIVERSITATIS OULUENSIS C Technica 383

#### KIMMO LASANEN

INTEGRATED ANALOGUE CMOS CIRCUITS AND STRUCTURES FOR HEART RATE DETECTORS AND OTHER LOW-VOLTAGE, LOW-POWER APPLICATIONS

Academic dissertation to be presented with the assent of the Faculty of Technology of the University of Oulu for public defence in OP-sali (Auditorium L10), Linnanmaa, on 24 May 2011, at 11 a.m.

UNIVERSITY OF OULU, OULU 2011

Copyright © 2011 Acta Univ. Oul. C 383, 2011

Supervised by Professor Juha Kostamovaara

Reviewed by Professor Andrea Baschirotto Professor Kari Halonen

ISBN 978-951-42-9454-9 (Paperback) ISBN 978-951-42-9455-6 (PDF) http://herkules.oulu.fi/isbn9789514294556/ ISSN 0355-3213 (Printed) ISSN 1796-2226 (Online) http://herkules.oulu.fi/issn03553213/

Cover Design Raimo Ahonen

JUVENES PRINT TAMPERE 2011

# Lasanen, Kimmo, Integrated analogue CMOS circuits and structures for heart rate detectors and other low-voltage, low-power applications.

University of Oulu, Faculty of Technology, Department of Electrical and Information Engineering; University of Oulu, Infotech Oulu, P.O. Box 4500, FI-90014 University of Oulu, Finland

Acta Univ. Oul. C 383, 2011 Oulu, Finland

#### Abstract

This thesis describes the development of low-voltage, low-power circuit blocks and structures for portable, battery-operated applications such as heart rate detectors, pacemakers and hearing-aid devices. In this work, the definition for low supply voltage operation is a voltage equal to or less than the minimum supply voltage needed to operate an analogue switch, i.e.  $V_{\text{DD}(min)} \le 2V_T + V_{ov}$ , which enables the use of a single cell battery whose polar voltage is 1-1.5 V. The targeted power consumption is in a range of microwatts.

The design restrictions for analogue circuit design caused by the low supply voltage requirement of the latest and future CMOS process technologies were considered and a few circuit blocks, namely two operational amplifiers, a  $G_m$ –C filter and a bandgap voltage reference circuit, were first designed to investigate their feasibility for the above-mentioned low-voltage and low-power environment. Two operational amplifiers with the same target specifications were designed with two different types of input stages, i.e. a floating-gate and a bulk-driven input stage, in order to compare their properties. Based on the experiences collected from the designed circuit blocks, an analogue CMOS preprocessing stage for a heart rate detector and a self-calibrating RC oscillator for clock and resistive/capacitive sensor applications were designed, manufactured and tested.

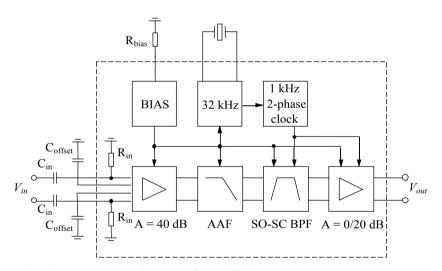

The analogue preprocessing stage for a heart rate detector includes a continuous-time offset-compensated preamplifier with a gain of 40 dB, an 8<sup>th</sup>-order switched-opamp switched-capacitor bandpass filter, a 32-kHz crystal oscillator and a bias circuit, and it achieves the required performance with a supply voltage range of 1.0-1.8 V and a current consumption of 3  $\mu$ A. The self-calibrating RC oscillator operates with supply voltages of 1.2-3.0 V and achieves a tunable frequency range of 0.2-150 MHz with a total accuracy of  $\pm 1\%$  within a supply voltage range of 1.2-1.5 V, a temperature range from -20 to 60 °C and a current consumption of less than 70  $\mu$ A @ 5 MHz with external high precision resistor and capacitor.

The measurement results prove that the developed low-voltage low-power analogue circuit structures can achieve the required performance and therefore be successfully implemented with modern CMOS process technologies with limited supply voltages.

Keywords: analogue circuits, heart rate detector, low-power, low-voltage, RC oscillator

Lasanen, Kimmo, Integroituja analogisia CMOS-piirejä ja -rakenteita sydämen sykkeen mittaukseen ja muihin matalan käyttöjännitteen pienitehoisiin sovelluksiin.

Oulun yliopisto, Teknillinen tiedekunta, Sähkö- ja tietotekniikan osasto; Oulun yliopisto, Infotech Oulu, PL 4500, 90014 Oulun yliopisto

Acta Univ. Oul. C 383, 2011

Oulu

#### Tiivistelmä

Tämä väitöskirja käsittelee matalan käyttöjännitteen pienitehoisten piirirakenteiden kehittämistä kannettaviin, paristokäyttöisiin sovelluksiin kuten esimerkiksi sykemittareihin, sydämen tahdistimiin ja kuulolaitteisiin. Matalalla käyttöjännitteellä tarkoitetaan jännitettä, joka on pienempi tai yhtäsuuri kuin analogisen kytkimen tarvitsema pienin mahdollinen käyttöjännite,  $V_{\mathrm{DD}(min)} \leq 2V_T + V_{ov}$ , joka mahdollistaa piirin toiminnan yhdellä paristolla, jonka napajännite on 1-1,5 V. Tavoiteltu tehonkulutus on mikrowattiluokkaa.

Piirirakenteiden suunnittelussa otettiin huomioon viimeisimpien ja lähitulevaisuuden CMOS-valmistusteknologioiden aiheuttamat matalan käyttöjännitteen erityisvaatimukset ja niiden pohjalta kehitettiin aluksi kaksi erilaista operaatiovahvistinta, GmC-suodatin, ja bandgap-jännitereferenssi. Operaatiovahvistimet toteutettiin samoin tavoitevaatimuksin kahdella eri tekniikalla käyttäen toisen vahvistimen tuloasteessa ns. kelluvahilaisia tulotransistoreita ja toisen tuloasteessa ns. allasohjattuja tulotransistoreita. Kehitetyistä rakenteista saatujen kokemusten pohjalta suunniteltiin, valmistettiin ja testattiin kaksi erilaista CMOS-teknologialla toteutettua mikropiiriä, jotka olivat analoginen esikäsittelypiiri sydämen sykkeen mittaukseen ja itsekalibroiva RC-oskillaattori resistiivisiin/kapasitiivisiin sensorisovelluksiin.

Sydämen sykkeen esikäsittelypiiri sisältää jatkuva-aikaisen, offset-kompensoidun esivahvistimen, jonka vahvistus on 40 dB, kytketyistä kapasitansseista ja kytketyistä operaatiovahvistimista koostuvan kahdeksannen asteen kaistanpäästösuodattimen, 32 kHz kideoskillaattorin ja bias-piirin. Esikäsittelypiiri saavuttaa vaadittavan suorituskyvyn 1,0 – 1,8 V käyttöjännitteellä ja 3  $\mu$ A virrankulutuksella. Itsekalibroivan RC-oskillaattorin käyttöjännitealue puolestaan on 1,2 – 3,0 V ja käyttökelpoinen taajuusalue 0,2 – 150 MHz. Ulkoista tarkkuusvastusta ja kondensaattoria käytettäessä oskillaattori saavuttaa ±1 % tarkkuuden 1,2 – 1,5 V käyttöjännitteillä ja -20 – 60 °C lämpötila-alueella virrankulutuksen jäädessä alle 70  $\mu$ A @ 5 MHz.

Mittaustulokset osoittavat, että kehitetyt matalan käyttöjännitteen pienitehoiset analogiset rakenteet saavuttavat vaadittavan suorituskyvyn ja voidaan näin ollen menestyksekkäästi valmistaa moderneilla matalan käyttöjännitteen CMOS-teknologioilla.

Asiasanat: analogiapiirit, matala käyttöjännite, pienitehoinen, RC-oskillaattori, sykemittari

# **Acknowledgements**

This thesis is based on research work carried out at the Electronics Laboratory of the Department of Electrical and Information Engineering, University of Oulu, during the years 1998–2008.

I wish to express my deepest gratitude to Professor Juha Kostamovaara, who has supervised this work, for his encouragement and guidance. I also thank my colleagues for the pleasant working atmosphere and their assistance. My family, relatives and friends deserve my warmest thanks for their patience and support during these years.

I wish to thank Professors Andrea Baschirotto and Kari Halonen for examining this thesis and Dr. John Braidwood for revising the English of the manuscript.

I would also like to thank Polar Electro, Fincitec, National Semiconductor Finland and Tekes for several interesting research projects, and the foundations Tekniikan edistämissäätiö, Tauno Tönningin säätiö and Seppo Säynäjäkankaan tiedesäätiö for providing direct financial support for this thesis.

Oulu, May 2011

Kimmo Lasanen

# List of symbols and abbreviations

AAF anti-aliasing filter A/D analogue-to-digital

ADC analogue-to-digital converter

ASIC application specific integrated circuit

ASP analogue signal processing

AV atrioventricular BD bulk-driven

BGR bandgap reference

BJT bipolar junction transistor

BPF bandpass filter BW bandwidth

C capacitor, capacitance

CM common-mode

CMFB common-mode feedback

CMOS complementary metal-oxide semiconductor

CMRR common-mode rejection ratio

CMR common-mode range CT continuous-time CP charge pump

DAC digital-to-analogue converter

DC direct current

DCG dynamic current generator

DDA differential difference amplifier

DR dynamic range

DSP digital signal processing

DT discrete-time

DTL dynamic translinear

DTMOS dynamic threshold voltage metal-oxide semiconductor

ECG electrocardiograph

EEG electroencephalograph

EEPROM electrically erasable programmable memory

EMG electromyography

EOG electro-oculography

FD fully-differential

FG floating-gate

FOM figure of merit

GBW gain-bandwidth product

G<sub>m</sub> transconductor

$G_m$ -C transconductor-capacitor

HR heart rate

HRV heart rate variability

IC integrated circuit

I/O inside/outside

IRN input referred noise

L length of a metal-oxide-semiconductor transistor

LED light emitting diode

LP low-power LV low-voltage

MOS metal-oxide-semiconductor

NEF noise efficiency factor

NMOS n-channel metal-oxide semiconductor (transistor)

OPA 2-stage operational amplifier

OTA operational transconductance amplifier

P part of an ECG waveform PCB printed circuit board

PGA programmable gain amplifier

PMOS p-channel metal-oxide semiconductor (transistor)

PPG photopletysmography ppm parts per million

PTAT proportional to absolute temperature

Q quality factor, part of an ECG waveform

QFG quasi-floating-gate

QRS part of an ECG waveform

R resistor, resistance, part of an ECG waveform

RC resistor-capacitor rms root mean square

S part of an ECG waveform

SA sinoatrial

SC switched-capacitor SE single-ended

SNDR signal-to-noise and distortion ratio

SNR signal-to-noise ratio

SO switched-opamp SoC system-on-chip

T part of an ECG waveform TC temperature coefficient

UV ultra-violet

VCO voltage controlled oscillator

W width of a metal-oxide-semiconductor transistor

WT wavelet transform

$A_{\nu}$  voltage gain

$C_{ox}$  gate capacitance per unit area  $f_{osc}$  frequency of oscillation

$g_{ds}$  conductance from drain to source  $g_m$  transconductance (from gate to drain)

$g_{mb}$  back-gate transconductance (from bulk to drain) K process constant (device characteristic constant)

k Boltzmann's constantm current mirror ratio

N number of stages, division factor

$Q_{FG}$  floating-gate charge q electron's charge

$t_D$  time delay

T temperature, time period  $T_{osc}$  period of oscillation  $V_{ov}$  overdrive voltage  $V_T$  threshold voltage

$\beta$  feedback factor

$\varphi$  phase

$\Sigma\Delta$  sigma-delta

σ standard deviationτ time constant

# List of original papers

This thesis consists of an overview and the following eight publications:

- I Räisänen-Ruotsalainen E, Lasanen K & Kostamovaara J (2000) A 1.2 V Micropower CMOS Op Amp with Floating-Gate Input Transistors, Proceedings of the 43rd IEEE Midwest Symposium on Circuits and Systems, Lansing, Michigan, USA, August 2000, 2: 794–797.

- II Lasanen K, Räisänen-Ruotsalainen E & Kostamovaara J (2000) A 1-V 5μW CMOS-Opamp with Bulk-Driven Input Transistors, Proceedings of the 43rd IEEE Midwest Symposium on Circuits and Systems, Lansing, Michigan, USA, August 2000, 3: 1038–1041.

- III Räisänen-Ruotsalainen E, Lasanen K, Siljander M & Kostamovaara J (2002) A Low-Power 5.4 kHz CMOS gm-C Bandpass Filter with On-Chip Center Frequency Tuning, Proceedings of the 2002 IEEE International Symposium on Circuits and Systems, Phoenix, Arizona, U.S.A., May 2002, 4: 651–654.

- IV Lasanen K, Räisänen-Ruotsalainen E & Kostamovaara J (2002) A 1-V, Self Adjusting, 5-MHz CMOS RC-Oscillator, Proceedings of the 2002 IEEE International Symposium on Circuits and Systems, Phoenix, Arizona, U.S.A., May 2002, 4: 377–380.

- V Lasanen K, Korkala V, Räisänen-Ruotsalainen E & Kostamovaara J (2002) Design of a 1-V Low-Power CMOS Bandgap Reference Based on Resistive Subdivision, Proceedings of the 45th IEEE Midwest Symposium on Circuits and Systems, Tulsa, Oklahoma, USA, August 2002, 3: 564–567.

- VI Lasanen K & Kostamovaara J (2004) A 1-V CMOS Preprocessing Chip for ECG Measurements, Proceedings of the IEEE International Workshop on BioMedical Circuits & Systems, Singapore, December 2004: S1/2 S1-4.

- VII Lasanen K & Kostamovaara J (2005) A 1-V Analog CMOS Front-End for Detecting QRS Complexes in a Cardiac Signal, IEEE Transactions on Circuits and Systems-I, December 2005, 52(12): 2584–2594.

- VIII Lasanen K & Kostamovaara J (2008) A 1.2-V CMOS RC Oscillator for Capacitive and Resistive Sensor Applications, IEEE Transactions on Instrumentation and Measurements, December 2008, 57(12): 2792–2800.

All papers were written by the author, except Paper I, which was written by Elvi Räisänen-Ruotsalainen, Dr. Tech. The circuits presented in Papers I and II were developed simultaneously by Elvi Räisänen-Ruotsalainen and the author, while the first writer of each paper was also responsible for most of the work behind it. Paper III was written by the author assisted by Elvi Räisänen-Ruotsalainen, who also designed the circuit. The circuit measurements for the fabricated chips were carried out by Markus Siljander, M.Sc. The circuit presented in Paper V was designed by Vesa Korkala, M.Sc. assisted by Elvi Räisänen-Ruotsalainen and the

author, who also wrote the paper. The work published in Papers IV, VI, VII and VIII was both done and written by the author.

# **Contents**

| Αl | bstra                                                       | ct         |                                                  |    |  |

|----|-------------------------------------------------------------|------------|--------------------------------------------------|----|--|

| Ti | iviste                                                      | elmä       |                                                  |    |  |

| A  | ckno                                                        | wledge     | ements                                           | 7  |  |

| Li | st of                                                       | symbo      | ols and abbreviations                            | 9  |  |

| Li | st of                                                       | origin     | al papers                                        | 13 |  |

| C  | onten                                                       | ıts        |                                                  | 15 |  |

| 1  | Intr                                                        | oduct      | ion                                              | 17 |  |

|    | 1.1                                                         | Motiv      | vation and aim of the work                       | 17 |  |

|    | 1.2                                                         | Struc      | ture of the thesis                               | 20 |  |

| 2  | Hea                                                         | rt rate    | e measurements                                   | 21 |  |

|    | 2.1                                                         | Chara      | acteristic of the ECG signal                     | 21 |  |

|    | 2.2                                                         | QRS        | detection methods and implementations            | 25 |  |

|    | 2.3                                                         | Prepr      | ocessing stage for a QRS detector                | 28 |  |

| 3  | RC                                                          | oscilla    | ntors                                            | 31 |  |

|    | 3.1                                                         | Linea      | r RC oscillators                                 | 32 |  |

|    | 3.2                                                         | Nonli      | inear RC oscillators                             | 34 |  |

|    | 3.3                                                         | RC os      | scillator implementations                        | 36 |  |

| 4  | Problems and solutions for LV/LP issues in analogue circuit |            |                                                  |    |  |

|    | desi                                                        | ign        |                                                  | 43 |  |

|    | 4.1                                                         | Dyna       | mic range of opamps                              | 44 |  |

|    |                                                             | 4.1.1      | Conventional input/output stages                 | 48 |  |

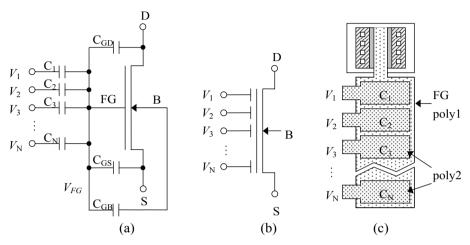

|    |                                                             | 4.1.2      | Floating-gate input stage                        | 57 |  |

|    |                                                             | 4.1.3      | Bulk-driven input stage                          | 60 |  |

|    | 4.2                                                         | Switc      | hes                                              | 61 |  |

|    | 4.3                                                         | Switc      | ched-opamps                                      | 65 |  |

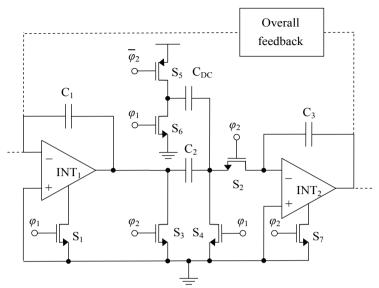

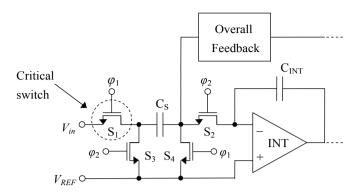

|    |                                                             | 4.3.1      | Switched-opamp integrators                       | 65 |  |

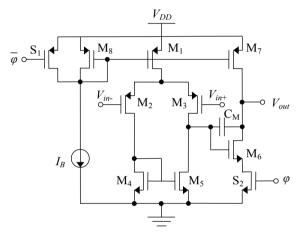

|    |                                                             | 4.3.2      | Internal circuit structures                      | 71 |  |

| 5  | Ove                                                         | erview     | of the original papers                           | 75 |  |

| 6  | Disc                                                        | Discussion |                                                  |    |  |

|    | 6.1                                                         | Analo      | ogue CMOS preprocessing stage for an HR detector | 79 |  |

|    |                                                             | 6.1.1      | Design choices                                   | 80 |  |

|    |                                                             | 6.1.2      | Performance                                      | 81 |  |

|    |                                                             | 6.1.3      | Future work                                      | 91 |  |

|    | 6.2                                                         | RC os      | scillator for clock and sensor applications      | 92 |  |

|    |                                                             | 6.2.1      | Design choices                                   | 95 |  |

|    | 6.2.2        | Performance | 96  |  |

|----|--------------|-------------|-----|--|

|    | 6.2.3        | Future work | 99  |  |

| 7  | 7 Conclusion |             |     |  |

| Re | eferences    |             | 105 |  |

| O  | riginal pap  | ers         | 117 |  |

# 1 Introduction

#### 1.1 Motivation and aim of the work

The main goal of this work has been to develop low-voltage (LV) and low-power (LP) integrated, analogue CMOS structures and circuit blocks for a heart rate (HR) meter, which is part of a personal portable sports/health watch. The aim is to be able to realize the integrated circuits with the latest (and future) CMOS processes with supply voltages of 1 – 1.5 V. These circuit blocks could also be used with minor modifications in other LV/LP applications, such as pacemakers and hearing-aid devices. Another goal of the work has been to design an accurate LV/LP RC oscillator, which can be used both as a capacitive/resistive sensor interface in sensor applications or as a clock circuit in discrete-time analogue/mixed-signal applications, such as hearing-aid devices.

An HR meter is a device which measures and calculates the average amount of heartbeats per minute. Heart rate is one of the four primary vital signs used by health professionals to evaluate health condition. The other signs are body temperature, blood pressure and respiration rate. Although it is possible to measure instant HR by hand, continuous electronic HR monitoring is more convenient, for example, for controlling patients during surgeries or sleep, or for controlling the intensity of training in sports activities, which is important when aiming for improved fitness level or weight reduction.

Commercial electronic HR monitors have already been on the market for about 30 years [1]. The first models were not portable, but, instead, they were implemented as a part of an exercise device, e.g. a treadmill or an exercise bike, which had a main unit with a display for HR and clock functions, and wired sensors which were attached to the finger, ear or chest of a person during the exercise. The sensor wires were considered both inconvenient and restrictive when using the device for outdoor sports. This fact resulted in the development of wireless HR meters which came on the market a few years later. The first wireless models had a chest belt with a transmitter and a wristwatch-like device for receiving and displaying the HR. The sensors and the heartbeat detection electronics were implanted in a chest belt, which was also generating and transmitting electrical or magnetic pulses for the receiver. The receiver counted the pulses and displayed the average amount of heartbeats per minute.

The basic transmitter/receiver construction of a wireless HR meter as described above has not changed much over the years, instead the amount of features and functions have increased tremendously. On top of basic clock and HR measuring functions a modern sports watch includes a lot of signal processing features, like saving heartbeat data and calculating different parameters from the data, which can then be read and analyzed directly from the display of the device or from a computer through a specifically designed interface and computer program. This development has been possible because of the development of digital techniques and process technologies and especially thanks to their continuously decreasing device sizes and line widths, which have made it possible to integrate more and more functions/electronics onto the same chip.

The speed of integrated circuits has increased as a result of miniaturization and at the same time the maximum allowable supply voltage has decreased. Reduction of the supply voltage is a result of reduced breakthrough voltages (due to reduced oxide thicknesses) and increased leakage currents (due to shorter channel lengths) of minimum size transistors. With the latest digital CMOS technologies the maximum supply voltage is already limited to about 1 V and the trend towards lower supply voltages is still continuing [2]. Low supply voltage is especially beneficial to digital integrated CMOS circuits, since their power consumption is proportional to the square of the supply voltage, i.e. reducing the supply voltage to half will reduce the power consumption to a quarter from its original value. In analogue CMOS signal processing the power consumption is not directly related to the supply voltage but, instead, it is basically set by the required signal-to-noise ratio (SNR) and the frequency of operation (or the required bandwidth) [3].

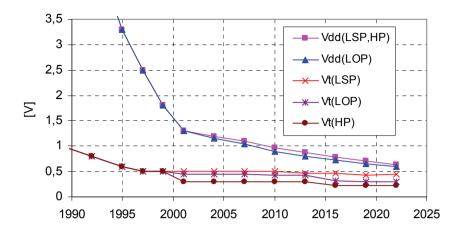

Although the supply voltages of digital CMOS processes have decreased in tandem with the miniaturization process, the same has not happened to the threshold voltages ( $V_T$ ) of MOS transistors. This can be seen from Fig. 1, which describes the present development and the predicted future development of supply voltages and threshold voltages for MOS transistors in digital process technologies as outlined in the International Technology Roadmap for Semiconductors (ITRS) [2]. Scaling of the threshold voltage is problematic, because a MOS transistor is not sharply switched off below its  $V_T$ , but instead there is a subthreshold current flowing through the transistor, which exponentially decreases when the gate-source voltage ( $V_{GS}$ ) approaches zero. When a transistor is switched off, the subthreshold current, i.e. a leakage current, has to be small

Fig. 1. Supply voltage and threshold voltage scaling projections from the ITRS 2001–2009 Roadmaps [2] for high performance (HP), low standby power (LSP) and low operating power (LOP) technologies.

enough (i.e.  $V_T$  large enough) to be tolerated by the design. Another fact supporting higher threshold voltages is the wide spread of  $V_T$  values for submicron technologies. The  $V_T$  limitation has led to the optimization of CMOS processes for different purposes (HP, LSP and LOP, see Fig. 1). In the worst case, the supply voltage is only about two times larger than the threshold voltages. For digital circuits this is still enough, but many traditional analogue circuits would no longer be able to operate with such a low supply voltage. Therefore, it is clear that there is a need to design new, low-voltage analogue circuit blocks that would operate with future CMOS process technologies under the same supply voltage as the digital circuit blocks.

The work presented in this thesis was carried out in several consecutive (industry-supported) Tekes projects, which focused on the research and development of analogue CMOS circuits and structures for LV/LP applications. An analogue CMOS front-end for an HR detector and an RC oscillator for clocking purposes and capacitive/resistive sensor applications were identified and selected as the two main applications of this work. Although these two applications are not directly related to each other, they still share the same LV/LP design problematics and can make use of similar circuit blocks. Therefore, the work was started with the design of basic analogue circuit blocks like operational amplifiers (hereinafter called opamps), voltage references and oscillator cores,

which were to be used as building blocks in the higher level designs. A primary goal was to achieve LV operation compatible with the supply voltage limitations of future CMOS process technologies. Another goal was to minimize power consumption of the developed circuit blocks in order to achieve long battery-life in portable applications. As a final outcome, the two main applications, i.e. an analogue CMOS front-end for an HR detector and an RC oscillator for clocking purposes and capacitive/resistive sensor applications, were designed, manufactured and tested.

#### 1.2 Structure of the thesis

The thesis is organized as follows: the electrical characteristics of an electrocardiogram (ECG) signal is described in Chapter 2, the latter part of which is devoted to reviewing different ECG measurement methods and circuit implementations, as well as introducing the general structure of a preprocessing stage for a QRS detector. The first part of Chapter 3 presents different types of RC oscillators and discusses their suitability for clocking and resistive/capacitive sensor interfaces, while the latter part concentrates on their circuit implementations. Chapter 4 highlights the circuit level LV/LP design problems related to the designed analogue integrated circuits and presents methods for solving them. An overview of the published papers is given in Chapter 5. Two LV/LP circuit level implementations and their performances are discussed in Chapter 6, the first part of which is devoted to an analogue preprocessing stage for a heart rate detector and the second part to an RC oscillator for clock and sensor applications. A conclusion of the presented work is given in Chapter 7.

# 2 Heart rate measurements

The operation of the heart is based on electrical waves which cause the heart muscle to pump blood. These electrical waves, which also pass through the body, can be measured with electrodes attached to the skin. The electrodes are made of conductive material, like metal or graphite, and the skin-electrode contact is often ensured using electrolytic paste. Contractions of the heart, i.e. heartbeats, are seen as spikes in the measured electrical waveform, which is called an electrocardiogram (ECG). Depending on the positioning of the electrodes, different projections of the ECG can be measured. Heart rate (HR) is an average number of heartbeats per minute and can be calculated from the spikes of the ECG.

HR can also be measured from the radial artery pressure (blood pressure) pulse using electroacoustical or optical sensors. An electroacoustical sensor can be realized with a piezo-microphone [4], which converts the blood pressure pulses into electric pulses. An optical sensor can be implemented with a light source and a receiver for measuring the amount of transmitted or reflected light, which is modulated by the blood pressure pulses. The modulated light signal is then converted into an electrical signal. This method is also called a photopletysmography (PPG) [5-9]. Because the blood pressure pulse measured with electroacoustical or optical sensors is in the same frequency and amplitude range as the added noise caused by motion artifacts [8, 10], the signal-to-noise ratio (SNR) of these methods cannot be improved by using conventional frequency selective filters. Moreover, the power consumption of optical methods is much higher than that of electroacoustical or electrical methods. This is due to the need for a light source, usually a light emitting diode (LED) with typical current consumption of a few milliamperes in continuous-time (CT) mode or a little bit less in pulsed mode. Therefore, the main stream portable/wearable HR meters have been realized with devices based on ECG.

## 2.1 Characteristic of the ECG signal

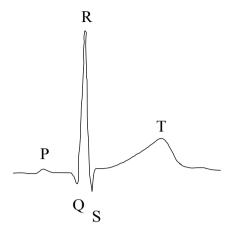

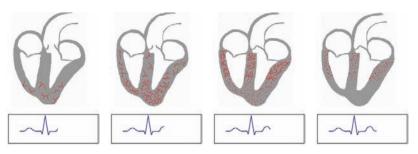

A typical healthy person's ECG, measured with two electrodes on both sides of the chest [11], is shown in Fig. 2. The amplitude and the shape of the waveform will vary depending on the positioning of the sensor electrodes, but there are certain parts of the waveform which can be recognized from all normal ECGs. These parts are named in alphabetical order as P, Q, R, S and T waves. Fig. 3 –

Fig. 2. Typical healthy person's electrocardiograph (ECG).

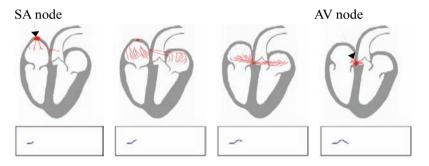

Fig. 3. Electrical activity of the heart; generation of the P wave [12].

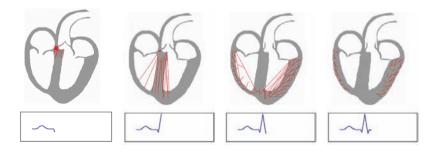

Fig. 4. Electrical activity of the heart; generation of the QRS complex [12].

Fig. 5. Electrical activity of the heart; generation of the T wave [12].

Fig. 5 (reprinted from [12]) shows how these waves are generated. The P wave represents atrial depolarization, where the electrical pulse starts from the sinoatrial (SA) node and proceeds to the atrioventricular (AV) node and spreads from the right atrium to the left atrium. The Q, R and S waves altogether form a QRS complex which corresponds to the depolarization of the ventricles. Because the ventricles have more muscle mass than the atriums, the QRS complex is larger than the P wave. It is also sharper because of increased conduction velocity. The T wave represents the repolarization of the ventricles.

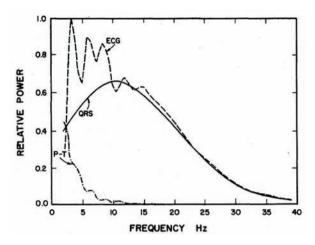

With a ground-free measurement setup [11] with two electrodes on both sides of the chest, the amplitude of the ECG can typically vary between  $100~\mu V$  and 2~mV. The ECG signal also contains a DC offset voltage of up to 300~mV, which develops across the skin-electrode interface due to an uneven distribution of anions and cations. The cardiac signal is generally considered to contain significant frequency components from 1 to 100~Hz, while the peak of the QRS complex is normally found between 10~and~15~Hz [13]. The averaged power spectra of a noiseless ECG, QRS complex and P- and T-waves (taken from [13]) are presented in Fig. 6.

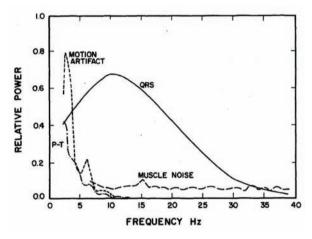

Practical signal quality is also degraded by disturbances such as electrical signals related to muscular activity (EMG), motion artifacts, variations in the quality of the skin-electrode contacts, mains noise (50 or 60 Hz) and also inherent signal variations, if these are large. The power spectra of muscle noise and motion artifacts in comparison with the QRS complex and P- and T-waves (taken from [13]) are presented in Fig. 7.

Since the QRS complex has the largest amplitude and the fastest rising and falling times when compared to other parts of the ECG waveform (Fig. 2), it is the easiest part to detect. As a contrast to clinical ECG measurements, in heart rate (HR) measurements preserving the fine details of the ECG waveform is not

Fig. 6. Averaged power spectra of ECG, QRS complex and P- and T-waves [13]  $\odot$  1994 IEEE.

Fig. 7. Averaged power spectra of QRS complex, P- and T-waves, muscle noise and motion artefacts [13]  $\odot$  1994 IEEE.

as important as reliable detection of the heartbeats, i.e. the QRS complexes. Therefore, the other parts of the ECG signal (P- and T-waves), as well as other disturbances, should be filtered out in order to enhance the detectability of the QRS complexes.

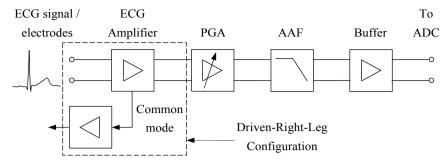

#### 2.2 QRS detection methods and implementations

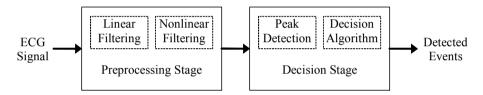

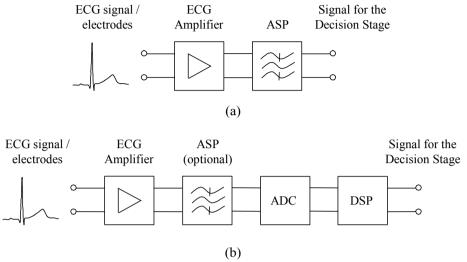

A generalized structure for a QRS detector, shown in Fig. 8, is a technology-free presentation which can be used as a starting point for any analogue or analogue/digital (mixed-signal) realization. The structure is divided into two main blocks, namely a preprocessing stage and a decision stage. The preprocessing stage performs linear and/or nonlinear filtering or transformations for the ECG signal in order to maximize the SNR of the QRS complexes. The decision stage then compares the preprocessed ECG signal against a threshold and makes a decision as to whether the detected event was a QRS complex or a noise peak. The decision rule or algorithm often needs the ECG signal preprocessed in a certain way, as this maximizes the performance of the decision stage. Therefore, the structure of the preprocessing stage has to be chosen according to the requirements of the selected QRS detection method.

Fig. 8. General structure of a QRS detector.

A large number of different QRS detection methods have been proposed in the literature including, for example, simple solutions based on linear filtering, peak detectors and comparators (or pulse shapers) with a threshold [14-21], methods including nonlinear transformations like differentiation [22-25], integration [26], a combination of differentiation, squaring and integration [27-30], a combination of differentiation and correlation [31, 32], methods based on optimized and matched filtering [33, 34], adaptive methods [35-38], wavelet transform [39-46], neural networks [47-49], combination of wavelet transform and neural-network-based adaptive filtering [50], and quite recently proposed methods based on mathematical morphology [51-53], voting algorithm [54], geometrical matching [55] and modified p-spectrum [56]. Most of these methods are developed for clinical use for finding and analyzing possible cardiac arrhythmias in real-time or from prerecorded ECG data. This task is normally carried out with a measurement setup consisting of an ECG preamplifier, analogue-to-digital converter (ADC) and a computer which implements and combines the QRS detection method (and

saving of the data) with a dedicated computer program. Therefore, these kinds of detectors are also called as software QRS detectors [57]. An overview of and comparison between several different detection methods is presented in [57] and [58].

The detection methods implemented by the software QRS detectors are often quite complex including features like calculation of the heart rate variability (HRV) and automated classification of abnormal heartbeats from the ECG, which makes them more suitable for stationary use in clinics for patient monitoring and diagnostic purposes. For ambulatory use, such as for controlling the intensity of a sporting exercise, the most important function is the real-time monitoring capability of the user's heart rate (HR). Therefore, the detector structure can be simpler but it has to be optimized against motion artifacts, which are the most dominant noise source while monitoring the HR of a moving target. Some of the above-mentioned methods designed for portable use were implemented with discrete components [24, 26, 29, 34] but, as expected, the lowest power consumption and the smallest physical size is obtained with a fully integrated, application specific integrated circuit (ASIC) [19-21, 25, 30, 33, 40, 42, 43, 45, 46]. Most of these integrated ORS detectors are based on linear filtering and peak detection with a threshold. Some of them also include one or more nonlinear transformations to enhance the QRS complexes. The rest of the reported solutions are based on a wavelet transform.

There are very few fully integrated QRS detectors reported in the literature. To the best of this author's knowledge, the only ones also including sensor interfaces are presented in [19-21]. The QRS detector chips presented in [19] and [20] are intended to be used in the wireless, sensor/transmitter unit (a chest belt) of a personal HR meter. These chips operate with supply voltages of 2.5 V – 3.3 V and consume 30  $\mu$ A (excluding the transmitter). The QRS detector chip developed in [21] is a sensor node with a piezo-microphone sensor and a transmitter interface, as suggested for a wireless health monitoring system. This chip operates with a supply voltage of 0.9 V and consumes 7.5  $\mu$ A in HR measurement mode. Because the ECG signal obtained by a piezo-microphone HR sensor is much higher than the signal obtained by electrodes (in the order of 100 mV<sub>(p-p)</sub> [59], whereas it is typically 1-2 mV<sub>(p-p)</sub> [20]), the preamplifier can be simpler since it does not necessarily need, for example, DC-offset compensation due to the low need for amplification. On the other hand, the operation of a piezo-microphone sensor is based on converting mechanical stress into electrical signals, which

makes it unsuitable for monitoring the HR during sporting activities because of motion-related disturbances.

An integrated analogue signal processor (ASP) for HR extraction is proposed in [25]. The ASP implements a robust peak detector based QRS detector, but it needs an external preamplifier. The ASP is implemented with a 0.5  $\mu$ m CMOS process and consumes 4.5 mA from a supply of  $\pm 2$  V.

The QRS detector presented in [30] is a digital system-on-chip (SoC) realization which is implemented using standard cells from the manufacturer's design library. The core of the design is a hard macro cell of a 32-bit reduced instruction set computer (RISC) with memory and bus controllers. The chip needs an external preamplifier and an ADC. The chip is implemented with a 0.18  $\mu$ m 1.8 V/3.3 V CMOS technology, but there is no information about the power consumption.

A programmable DSP ASIC for HR measurements is presented in [33]. This chip also needs an external preamplifier and an ADC. The chip is implemented with a  $1.0~\mu m$  CMOS technology, but neither the supply voltage nor the power consumption has been reported.

An analogue QRS detector chip based on wavelet transform (WT) is presented in [40]. This chip implements a WT, an absolute value circuit, a peak detector and a comparator by means of dynamic translinear (DTL) circuit technique [60]. The WT system has 5 parallel scales and its power consumption is 55 nW per scale from a 2-V supply. This chip is implemented with a semi-custom bipolar IC process.

The rest of the published QRS detectors [42, 43, 45, 46] are based on digital WT and they also need external preamplifiers and ADCs. The design presented in [43], which is a developed version of [42], is implemented with 0.13 µm CMOS technology with supply voltage of 1.2 V. It includes a wavelet filter bank and a generalized likelihood ratio test with a threshold function. Estimated power consumption based on simulations in alert and normal mode is 114 nW and 37.9 nW, respectively. The QRS detector chip presented in [45] contains a wavelet filter bank and a multi-scale multiplier with a threshold function and it is implemented with 0.18 µm CMOS technology. Simulated power consumption is 644.9 nW, when all wavelet filters are active and 318.4 nW in normal operation, when half of the filters are switched off. It is worth mentioning here that over 90% of the power consumption of this chip is caused by leakage currents, which are a serious problem with deep sub-micron technologies. The ECG signal processor proposed in [46] includes a wavelet filter bank and denoising block

followed by heartbeat rate prediction and classification blocks. This chip is an SRAM-based ASIC architecture, which is realized with 0.18  $\mu$ m CMOS technology. The chip consumes 29  $\mu$ W from a 1-V supply.

All of the above-mentioned QRS detectors are aimed at non-invasive measurement of the HR, but modern implantable pacemakers, like the one presented in [61], also include an HR measurement function. In pacemaker applications the supply voltage is usually higher, in the order of 2.8 V, because of the need to generate high-voltage ( $\sim 5$  V) pulses to stimulate the heart muscle (for example, to initiate a heart-beat). The high-voltage pulse is generated with a capacitive voltage multiplier. Because the pacemaker is implanted inside the body of the user, the pacemaker chip has to be optimized for very low-power consumption in order to achieve a long battery-life. Therefore, the chip proposed in [61] is implemented with a special 0.5  $\mu$ m multi- $V_T$  process, consuming only 8  $\mu$ A from a 2.8-V supply. Although the structure of the QRS detector is not presented it is presumably not compatible with very low supply voltages.

As a final note, it can be concluded that several integrated low-power (LP) analogue/digital QRS detectors have been reported in the literature, but only a few of them are capable of very low supply voltage operation of 1 V or less. Moreover, none of them contains a preamplifier with adequate performance for ECG measurements operating with 1 V or less. Since the preprocessing stage of the QRS detector always needs an analogue interface between the ECG sensors and the analogue or digital signal processor, it is also important to find a way to implement that in a low-voltage (LV) environment. Therefore, this work has been focused on developing analogue LV/LP circuit blocks and a sensor interface for the preprocessing stage of a QRS detector.

### 2.3 Preprocessing stage for a QRS detector

As described in Chapter 2.2 a preprocessing stage performs linear and/or nonlinear filtering/transformations for the ECG signal in order to maximize the SNR of the QRS complexes (Fig. 8). A practical realization also includes an ECG amplifier in front of the preprocessing stage. The amplifier is needed to increase a weak ECG signal, which may vary from 100  $\mu$ V to 2 mV measured with electrodes, at a reasonable level for further processing. The next stage is either an analogue signal processing (ASP) block or an analogue-to-digital converter (ADC) followed by a digital signal processing (DSP) block. It is also possible to do one part of the signal processing in analogue domain and the other part in digital

domain. The structure of an integrated preprocessing stage with an ECG amplifier is shown in Fig. 9.

Fig. 9. (a) Analogue and (b) analogue/digital (mixed-mode) preprocessing stage structure for a QRS detector.

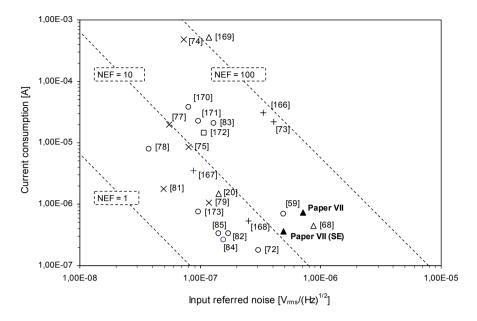

Although it would be possible to implement the ECG amplifier using discrete components [62] and the preprocessing stage with microprocessors [63-65], it would result in larger physical size and higher power consumption when compared to a custom-made ASIC implementation developed in this work. Existing realizations of integrated ECG preprocessing stage structures can be divided into two main categories, namely: 1) interfaces for implantable pacemakers, and 2) interfaces for portable/wearable ECG/HR monitoring devices. Although there are some very low-power designs aimed for pacemaker interfaces [61, 66-71], they are designed for higher supply voltages ranging from 1.5 to 2.8 V, which makes them incompatible with the latest CMOS process technologies. Also, most of the other types of recently published LP ECG/biomedical sensor interfaces [71-81] operate with fairly high supply voltages, but there are a few biosignal acquisition interface chips [82-86] which can also operate with a supply of less than 1V. Therefore, the prerequisites for designing the entire integrated QRS detector (including an ECG preamplifier, an ASP or a DSP with an ADC and a transmitter) operating with supply voltages of 1 - 1.5 V exist.

Since the desired supply voltage range is very low, it poses many circuit level design challenges for the analogue part of a QRS detector. The main problems are:

1) a limited dynamic range (DR) and consequently 2) a reduced signal-to-noise ratio (SNR) of the analogue interface connected to the ECG sensors and 3) an insufficient drive voltage to operate all switches of conventional switched capacitor (SC) circuits. These problems are discussed in more detail in Chapter 4.

The problems related to the limited DR and SNR of the QRS detector are reduced to the signal swing limitations of the used opamps, and more specifically to their input stages, which are discussed in Chapters 4.1.1 – 4.1.3. In order to achieve an adequate DR for the QRS detector, two opamps with different types of input stages, i.e. floating-gate (FG) and bulk-driven (BD) input stages, have been designed and published in Papers I and II to study their possible advantages over the opamps equipped with conventional input stages.

The problems and solutions concerning analogue switches in SC circuits are introduced in Chapter 4.2 and the concept of a switched-opamp is presented in Chapter 4.3. The idea behind the switched-opamp circuit is to achieve a lower minimum supply voltage for an SC circuit by removing the need for critical series switches from the signal path. A critical switch is a switch which needs to conduct the whole signal swing, for example, from the output of an opamp to a sampling capacitor. The minimum possible supply voltage for an SC circuit can be achieved if all switches can be switched either against the positive or the negative (usually ground) supply voltage. As a result of these studies, a whole LV/LP QRS detector interface, including a sensor interface and a switched-opamp switched-capacitor (SO-SC) filter, is presented in Papers VI and VII, while the design choices, performance and future work of this design are also discussed in Chapter 6.1.

# 3 RC oscillators

A low-voltage low-power (LV/LP) RC oscillator was chosen as another important application to be developed in this work. The aim was to design an initially accurate RC oscillator (which does not need any calibration or additional reference) that could be used both as a capacitive/resistive sensor interface in sensor applications or as a clock circuit in discrete-time (DT) analogue/mixed-signal designs. An RC oscillator could also be used in communication links such as Universal Asynchronous Receiver Transmitter (UART) circuits if frequency variation is kept within  $\pm 1\%$ . Therefore an accuracy of  $\pm 1\%$  is considered adequate for the foreseen clocking purposes and the tuning/sensing range of  $\pm 1$  decade enough for external circuit elements/sensors R and C. The target supply voltage for the RC oscillator is 1-1.5 V, and the power consumption is in a range of microwatts.

Traditionally RC oscillators have been used in applications like tone generators, alarms and flashing lights where only moderate accuracy is required. This is due to the fact that an accurate operating frequency and a small temperature drift are much easier to realize with a crystal oscillator. Commercially available quartz crystals and crystal oscillators can easily achieve an initial accuracy of 10 ppm with a temperature drift of less than 0.05 ppm/°C. Therefore, they are the most frequently used solution for time keeping and clocking purposes. The benefits of an RC oscillator over a crystal oscillator are the possibility of adjusting the frequency and integrating all components onto one chip. Passive components R and C are also much cheaper than quartz crystals, which might be a selection criterion especially in large production series. In order to achieve a good accuracy with an RC oscillator, circuit elements R and C must be either external precision components or trimmable integrated components. In both cases the expected frequency accuracy and temperature drift, which are typically within few percent, are quite modest when compared with the performance of a crystal oscillator. However, an RC oscillator can be used as a clock generator in many applications such as microprocessors, hearing-aid devices, pacemakers, sensor ICs and other SoCs where extreme accuracy is not required.

Recently, interest has grown in RC oscillators, especially in sensor applications where either R or C is replaced with a resistive or a capacitive sensor. With these sensors it is possible to measure, for example, pressure, temperature and humidity [87, 88]. The idea is to convert changes in resistance or capacitance

to changes of frequency, which is actually one kind of an analogue-to-digital (A/D) conversion. Depending on the application, the output can be used, for example, to adjust a process variable, as an alarm when preset threshold levels are exceeded or by displaying a parameter value under measurement.

There are several ways to realize an RC oscillator depending on the requirements of the application. Referring to their output, classical RC oscillators can be divided into two main categories: linear (sine-wave) and nonlinear (square-wave, triangular or sawtooth) oscillators. The most common topologies of both categories are presented in the following subchapters.

#### 3.1 Linear RC oscillators

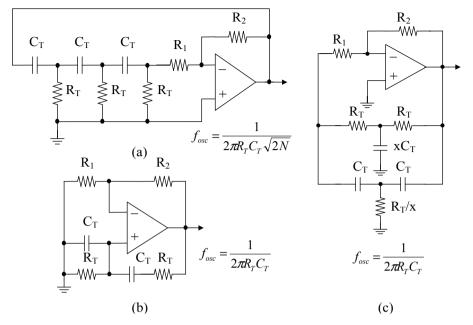

A linear (sine-wave) RC oscillator consists of two parts made up of a tuned RC network and an amplifier in a feedback configuration. The amplifier can be either an opamp or a simpler amplifier stage with one or a few more transistors. The most common linear RC oscillators, namely a phase-shift oscillator, a Wien bridge oscillator and a Twin-T oscillator, are presented in Fig. 10.

In order to operate as an oscillator, all these circuits need to meet Barkhausen's criterion, which states that the loop gain at the oscillation frequency is equal to unity and the total phase shift around the loop is zero or a multiple integer of  $2\pi$  (360°), i.e.  $n \cdot 2\pi$  ( $n \cdot 360$ °), where n = 0,1,2,... The operation principle of each oscillator topology is briefly explained in the following paragraphs and a more detailed analysis of these circuits can be found, for example, from [89].

In case of a phase-shift oscillator, the frequency of oscillation,  $f_{osc}$ , is defined by the time constant  $\tau = R_T C_T$  and the number (N) of consecutive RC stages in a feedback loop. The oscillator settles to a frequency where the total phase shift of the loop is 0°. One part of the total phase shift is due to the inverting amplifier (-180°) and the other part due to the RC chain (+180°) in a feedback loop. The minimum amount of RC stages capable of producing a 180° phase shift at a finite frequency is three. Therefore, the phase shift in case of three consecutive RC stages is 60° per stage. For a loop gain of 1, the opamp's gain has to be  $|A_v| = R_2/R_1 \ge 29$  and  $R_I$  must be sufficiently large, for instance  $R_1 > 10R_T$ , to minimize the loading of the opamp.

Fig. 10. Sine-wave RC oscillators: (a) a phase-shift oscillator, (b) a Wien bridge oscillator and (c) a Twin-T oscillator. Amplitude regulation circuits are not shown.

The output frequency of a Wien bridge oscillator is set by two RC stages. The first one is connected between the positive input and analogue ground and the other one between the positive input and the output of the amplifier. The loop gain is set by two resistances on the negative feedback path of the amplifier. When  $R_2/R_1 \ge 2$ , the loop gain of the whole circuit is equal to or larger than 1 and the circuit operates as an oscillator.

A Twin-T topology has two parallel connected RC networks in a feedback configuration. Altogether, these branches form a notch filter which is tuned at the oscillation frequency defined by the time constant  $\tau = R_T C_T$ . For a loop gain equal to 1, the gain,  $A_v$ , of the opamp and values for components  $xC_T$  and  $R_T/x$  have to be chosen according to  $A_v = (x + 2/x + 1)/(1 - 2/x)$  [89]. If the Twin-T oscillator is designed with x = 2, the opamp requires an infinite gain. Hence, for practical realizations  $x \ge 2.5$  is more sensible.

Although not shown in Fig. 10, all of the presented topologies need some sort of an amplitude regulation circuit to set the loop gain exactly to unity to maintain a sinusoidal waveform at the output of the oscillator. There are several different methods for adjusting the loop gain, the easiest being the use of some kind of a

nonlinear element in the feedback loop, which causes the loop gain with small amplitude levels to be larger than unity and with too large amplitude levels less than unity. The simplest possible realization of this type of nonlinearity is an amplifier with an amplitude regulated output, although for low distortion and precisely controlled amplitude, a more sophisticated nonlinearity is required.

Because the output frequency of all topologies presented in Fig. 10 is determined by multiple resistors and capacitors with certain component ratios, they are more suitable for clocking than sensor applications.

#### 3.2 Nonlinear RC oscillators

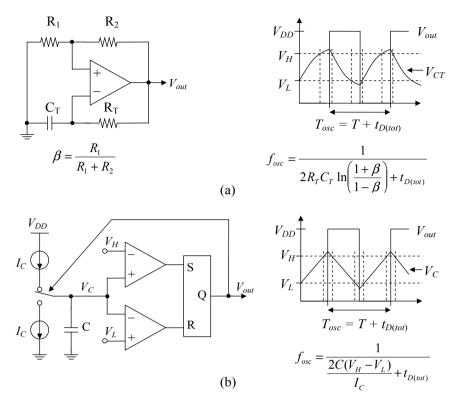

Nonlinear (square-wave, triangular or sawtooth) RC oscillators are often called relaxation oscillators. The term "relaxation" refers to charging and discharging phases of a capacitor. There are many types of relaxation oscillators, starting from simple two-transistor multivibrator circuits to more complex topologies, but they all share the same operation principle. Fig. 11 presents two examples of a relaxation oscillator, which are astable multivibrator circuits based on a single comparator and a commonly used relaxation oscillator topology which allows the adjustment of its parameters more freely.

The core of the astable multivibrator circuit [90] presented in Fig. 11 (a) is based on a Schmitt trigger, which consists of a comparator and two resistors, R<sub>1</sub> and R<sub>2</sub>, in a positive feedback configuration. If the positive and the negative supply voltage of the comparator are set to  $V_{DD}$  and 0 V and the analogue ground voltage to  $V_{DD}/2$ , the resistors will set the triggering points (hysteresis) of the comparator to  $V_H = (1 + \beta)V_{DD}/2$  and  $V_L = (1 - \beta)V_{DD}/2$ , where  $\beta$  is the feedback factor of the comparator, i.e.  $\beta = R_1/(R_1 + R_2)$ . In order to use the circuit as an oscillator, a capacitor C<sub>T</sub> is connected from the negative input terminal to the analogue ground and a resistor R<sub>T</sub> between the negative input and the output terminal of the comparator. If the output voltage of the comparator at a given moment is at  $V_{DD}$ , the voltage at the positive input terminal of the comparator is at  $V_H$  and  $C_T$  is charged through  $R_T$  (with a time constant  $\tau = R_T C_T$ ) until voltage at the negative input terminal exceeds  $V_H$ . At this point the comparator changes its output state from  $V_{DD}$  to 0 V and the voltage at the positive input settles to  $V_L$ , which causes  $C_T$  to be discharged through  $R_T$  until the voltage across  $C_T$  falls below  $V_L$  and the comparator will change its state again.

Fig. 11. Nonlinear (square-wave) RC oscillators: (a) an astable multivibrator based on a Schmitt trigger and (b) a relaxation oscillator.

The output frequency  $f_{osc}$  of the oscillator presented in Fig. 11 (a) is ideally a function of the feedback factor  $\beta$  and the time constant  $\tau = R_T C_T$ . In practice,  $f_{osc}$  is also dependent on  $V_{DD}$  variations and the comparator's state-to-state transition delays  $(t_{D(tot)})$ , which together add up to the oscillation period. Variations in  $V_{DD}$  will also affect the threshold voltages  $V_H$  and  $V_L$  and the charging/discharging current of  $C_T$ . Therefore, the described simple multivibrator circuit is more suitable for low frequency applications with low accuracy requirements, such as flashing lights and tone alarms.

Another relaxation oscillator, presented in Fig. 11 (b), is a commonly used topology which consists of a digital SR latch driven by two comparators with presettable threshold voltages, a timing capacitor and a constant current sink/source. In this case, the timing capacitor is charged and discharged with a constant current  $I_C$ , which can be set, for example, by a resistor in a bias circuit. The voltage  $V_C$  across the capacitor is compared against two threshold voltages

$V_H$  and  $V_L$  with two comparators. Whenever the capacitor voltage reaches either of the thresholds, the SR latch toggles and reverses the direction of the capacitor current. Ideally, the oscillation frequency would be directly proportional to the capacitor current and inversely proportional to the capacitor value and the difference of the threshold voltages, but again the delays  $(t_{D(tot)})$  introduced by the comparators and the latch of the level detection circuit (causing overshooting of the threshold voltages) add up to the output period, which causes the actual oscillation frequency to be lower than ideal. This effect increases towards higher frequencies.

Since it is possible to set the output frequency of a relaxation oscillator with only one resistor and capacitor (or corresponding sensor element), it is a better choice for sensor applications than the linear topologies presented in Chapter 3.1. Relaxation oscillators can also be used as clock generators, which allow the clock frequency to be tuned with minimum amount of passive components. However, the delays introduced by the comparators add up to the period which limits the frequency accuracy of this type of oscillator at high frequencies.

The next chapter summarizes the state-of-the-art LP RC oscillators suitable for both sensor and clock applications. All presented topologies are based on the relaxation oscillator principle.

### 3.3 RC oscillator implementations

Since the introduction of the 555 timer, RC oscillators have been used in commercial applications as clock, pulse, delay and ramp generators. The 555 timer is based on a relaxation oscillator topology, presented in Fig. 11 (b), and is available both as bipolar and CMOS versions. Although the latest CMOS versions are able to operate with supply voltages as low as 1.5 V (LMC555) or even 1 V (TLC551, which has the same pinout and functionality as the 555 type of timer), their maximum operating frequency is only up to a few MHz because of the delays present in the comparators and the parasitic capacitances and resistances related to the I/O timing pins. Furthermore the current consumption of general purpose RC timers is typically quite high, up to  $1-10~\rm mA$ , which is too high for LP applications. There are also some LP timers, such as LTC6906, which consumes only  $12~\rm \mu A$  at  $100~\rm kHz$  operating frequency, but its minimum supply voltage is  $2.25~\rm V$  and it can operate only up to  $1~\rm MHz$  frequency.

On the other hand, the overall frequency accuracy of the above-mentioned RC oscillators depends not only on the values of passive circuit elements R and C

but also on the comparator's "high-to-low" and "low-to-high" transition delays, both of which are functions of supply voltage and temperature. These delays will decrease the frequency stability at high frequency in clock applications and the measurement linearity in resistive or capacitive sensor applications. Therefore, the circuit topologies presented in these commercially available ICs do not satisfy the requirements set for this work.

If an RC oscillator is used only for clocking purposes, circuit elements R and C can be realized with either external or integrated components. In case of a fully integrated RC oscillator, the value of the RC time constant without tuning can vary up to ±40%. In addition, the temperature coefficient (TC) of integrated resistors is quite large, in the order of 1000 – 3000 ppm/°C [91], which also has to be taken into account when designing an accurate clock generator. On the other hand, the TC of integrated capacitors is negligible. Therefore, an accurate integrated RC oscillator should not only provide some kind of temperature compensation scheme for the resistor but also the opportunity to tune the operating frequency of the whole RC oscillator. Another way is to use an accurate and temperature compensated external time constant RC instead of integrated R and C.

Table 1 summarizes the performance of commercial and other published relaxation oscillators with respect to the most important parameters for an RC oscillator set in this current work. Commercial timer circuits are listed above and other published relaxation oscillators below the dashed line.

The design presented in [92] is a relaxation type 32-kHz RC oscillator with internal C and external R without tuning. The initial frequency accuracy of the oscillator (which is not reported) mainly depends on the process variation of the integrated C and the delay of the comparator. The comparator alone causes an estimated additional delay of 13% for the oscillation period at 32-kHz operating frequency. The measured standard deviation for the chip-to-chip variation is about 4.3%, the supply voltage dependence -2.3%/V from 2.5 to 5 V and the temperature drift -3% from -20 to 70 °C.

Reference [93] presents a fully integrated RC oscillator, which includes a digitally trimmed resistor to eliminate the process variations and a simple temperature drift compensation circuit realized with a combination of an integrated resistor with a negative TC and a transistor with a positive TC. Simulation results show that the output frequency span with worst case simulation corner parameters with and without trimming is  $\pm 0.5\%$  and  $\pm 40\%$ , respectively.

Table 1. Features of commercial and other published relaxation oscillators.

| Туре                | $V_{DD}$     | I <sub>tot</sub> | f <sub>max</sub> | Accuracy            |

|---------------------|--------------|------------------|------------------|---------------------|

| LMC555              | 1.5 – 15 V   | < 150 µA @ 1.5 V | 3.0 MHz @ 5 V    | -                   |

| TLC551              | 1.0 – 15 V   | < 150 µA @ 1.0 V | 1.8 MHz @ 5 V    | -                   |

| LTC6906             | 2.25 – 5.5 V | 12 μA @ 100 kHz  | 1 MHz            | ±0.5%               |

| [92]                | 2.5 – 3.5 V  | 2.1 μA @ 2.8 V   | 32 kHz           | < 10% <sup>1)</sup> |

| [93] <sup>2)</sup>  | 4.5 – 5.5 V  | -                | 2 MHz            | ±0.5% 3)            |

| [94]                | 1.1 – 2.0 V  | 7.7 µA @ 1.2 V   | 1.2 MHz          | ±4.1% 1)            |

| [95, 96]            | 0.8 V        | 770 nA           | 50 kHz           | ~30%                |

| [97, 98]            | 1.7 – 1.9 V  | 24 μΑ            | 14 MHz           | ±0.9% 1)            |

| [99]                | 3.0 - 5.0 V  | 133 μΑ           | 12.8 MHz         | ±5% 3)              |

| [100]               | 2.0 – 2.75 V | -                | 36 MHz           | ±2% 3)              |

| [101] <sup>2)</sup> | 3.0 – 3.6 V  | 400 µA           | 1 MHz            | 1% <sup>3)</sup>    |

| [102]               | 1.8 – 2.5 V  | < 2.14 µA        | 2 MHz            | ±2.5% 3)            |

| [103] <sup>2)</sup> | 0.9 – 1.1 V  | 660 nA           | 307.2 kHz        | ±6.1% 3)            |

| [104]               | 2.7 – 6.0 V  | -                | 103 MHz          | -                   |

| [105]               | 1.25 – 1.5 V | 750 µA           | 24 MHz           | < 4% <sup>3)</sup>  |

<sup>&</sup>lt;sup>1)</sup> Process variation not included. <sup>2)</sup> Only simulated results. <sup>3)</sup> After tuning.

Also, the temperature drift between 0 and 80 °C has been reduced from -5.65...13.90% to -0.75...0.05%. The reported supply voltage dependency is between 1.00 and -0.50% from 4.5 to 5.5 V. Therefore, it seems that with tuning it is possible to achieve about 1% total accuracy but the drawback is that every chip needs to be tuned individually.

In order to avoid tuning and the use of external references, some integrated oscillator topologies [94-98], presented in the literature, use an internal voltage reference to set the oscillation frequency. In [94], the voltage reference is realized with a constant- $g_m$  bias generator, which provides the input voltage for a ring-oscillator type of a VCO. The capacitors are implemented with gate-capacitances of grounded NMOS transistors in between the inverter stages of the VCO. Because the integrated capacitor values are not tuned, the output frequency of 1.25 MHz is on average 4.2% larger than expected by the simulations. Furthermore, this circuit has quite a large supply voltage dependence of  $\pm 4.1\%$  when the supply voltage is swept from 1.1 V to 2.0 V, which is mainly due to the constant- $g_m$  voltage reference circuit being not as stable as a bandgap reference (BGR) circuit. The temperature drift is not mentioned. The oscillator consumes 7.7  $\mu$ A (9.2  $\mu$ W) from a 1.2 V supply voltage. By comparison, the clock generator presented in [95, 96] uses a BGR circuit for generating the reference voltages and currents for a relaxation oscillator. Because the integrated capacitors are not tuned,

the simulated 1σ and 3σ variations of the output frequency are 4% and 11.85%, respectively, the TC 842 ppm/°C from 0 to 80 °C and the supply voltage variation -2.5%/V from 1 to 1.5 V. The measured chip-to-chip variation with a 0.8 V supply voltage is large, close to 30%, and the operating frequency starts to decrease rapidly above 0.8 V, which behavior the authors could neither explain nor reproduce by simulations. The measured TC from 20 to 60 °C is 0.3%/°C.

A relaxation oscillator presented in [97, 98] is a fully integrated RC oscillator, which uses a voltage averaging feedback circuit with a voltage reference proportional to supply voltage. This circuit is shown to be quite insensitive to supply voltage variations because of the operation principle. On the other hand, the temperature dependency relies on the TC of the integrated R and the total accuracy on both R and C in the oscillator core. The oscillator achieves a measured TC of  $\pm 0.75\%$  from -40 to 125 °C and a supply voltage variation of  $\pm 0.16\%$  from 1.7 to 1.9 V. Neither the chip-to-chip variation nor the absolute accuracy of the output frequency is published.

In references [99-101], the use of an internal voltage reference has been combined with trimming of the output frequency. In [99], a BGR is used for generating temperature compensated reference voltages for the comparators and currents for charging/discharging the capacitors in a relaxation oscillator. The timing capacitor is comprised of an 8-bit binary-weighted capacitor array to cancel out the effects of process variations. This oscillator achieves  $\pm 5\%$  total frequency accuracy including process variations, supply voltage variation from 3 to 5 V and temperature range of -40 to 125 °C without any external components. The same idea has been utilized in [100], which presents a relaxation oscillator with a BGR and a 5-bit capacitor array. This oscillator operates with a supply voltage down to 2 V and it achieves  $\pm 5\%$  frequency accuracy with a supply voltage range of 2.5 V  $\pm 10\%$  and a temperature range from 0 to 80 °C without external components.

The RC oscillator proposed in [101] uses an external resistor, an integrated capacitor and a reference voltage based on a resistor ratio with a tuning circuit. The use of an external resistor ensures a low temperature variation (if a low-TC component is used) and the tunable reference voltage can be used to cancel out the process variations. This oscillator achieves a total simulated frequency accuracy of 1% with supply voltage variation of 3.3 V  $\pm 10\%$  and a temperature range from -40 to 125 °C.

Two LP RC oscillators for capacitive sensor applications are presented in [102, 103]. The oscillator, described in [102], consists of a source-coupled CMOS

multivibrator, a proportional-to-absolute-temperature (PTAT) bias circuit and a two-stage comparator. The bias circuit is provided with a programmable resistor matrix and the oscillator with a capacitance matrix to enable calibration. After calibration the oscillator achieves an operating frequency of 2 MHz with a total accuracy of  $\pm 2.5\%$  including a supply voltage variation of  $\pm 10\%$  and a temperature range from -35 °C to +85 °C. The typical power consumption with a 1.8-V supply voltage at room temperature is 3.0 µW. The circuit operates with supply voltages from 1.8 to 2.5 V. The oscillator presented in [103] is a modified version of [102] and it consists of two parallel tunable oscillators (only one operates at a time) with different operating frequencies to cover a larger range of operating frequencies. Because of a lower supply voltage of 1 V used by this design, the floating capacitance matrix of [102] has been replaced with a fixed capacitor and tuning is accomplished with a resistor matrix. The simulation results for this double-mode oscillator in modes 1 and 2 show a frequency stability of 24.6 kHz  $\pm 10.7\%$  and 307.2 kHz  $\pm 6.1\%$  with a supply voltage variation of 1 V  $\pm 10\%$  and a temperature range from -40 to 85 °C. The current consumption in modes 1 and 2 are 210 nA and 660 nA, respectively.

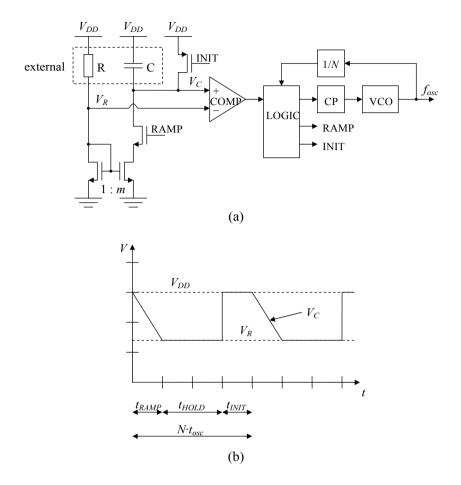

Reference [104] presents an RC oscillator topology which places a ringoscillator type of VCO in a feedback loop of a relaxation type RC oscillator. This oscillator samples its own period and compares it to the RC time constant. One advantage of this operation principle is that it uses a frequency divider to separate the operating frequency of the VCO from the charging/discharging frequency of the capacitor. As a result, the output frequency of the oscillator and the values for passive components can be selected more freely. Another advantage is that the negative feedback loop corrects all variations caused by temperature, supply voltage and process variations. The total accuracy of the oscillator, presented in [104], depends only on the RC time constant itself, added with the accuracy of the frequency divider and a current mirror ratio. Because the division ratio can be assumed ideal, the final accuracy reduces to the accuracies of the RC time constant and the current mirror ratio. The reported performance (excluding variations of external components R and C) shows that the maximum operating frequency is 103 MHz, the supply voltage sensitivity 3,430 ppm/V or 1.13% from 2.7 V to 6.0 V and the temperature sensitivity 57.1 ppm/°C (the temperature range is not reported).

The RC oscillator, presented in [105], uses the operation principle described in [104] with an added tuning option. After tuning the oscillator achieves a total frequency accuracy of 4%, including process variations, supply voltage variations

from 1.25 to 1.5 V, temperature variations from -40 to 85 °C and 1% component variation in external RC time constant.

As a conclusion for this review, it may be noted that there are several RC oscillator topologies which satisfy the requirements of LV/LP operation but most of them do not reach the desired total frequency accuracy of  $<\pm1\%$  even if tuned, which was one of the goals in this particular piece of work. Without tuning, none of the LV/LP designs is even close to this target. The most promising topology of the RC oscillators described above is the one presented in [104], which allows choosing the component values and the frequency of operation more freely. This is an important feature when aiming for low power consumption, high frequencies or an optimized sensor interface with a certain impedance range. Therefore, the idea presented in [104] has been adopted for the design of an accurate LV/LP RC oscillator for clock and sensor applications, two versions of which are presented in Papers IV and VIII. The design choices, performance and future work of this design are presented in Chapter 6.2.

# 4 Problems and solutions for LV/LP issues in analogue circuit design

This chapter concentrates on practical circuit level design problems and their viable solutions concerning two main applications, i.e. a low-voltage, low-power (LV/LP) preprocessing stage for a heart rate detector and an LV/LP RC oscillator, developed in this work. Since the desired supply voltage range set for this work is very low, i.e.  $V_{DD(min)} \leq 2V_T + V_{ov}$ , it poses many design challenges for both continuous-time (CT) and discrete-time (DT) analogue signal processing (ASP) circuits.

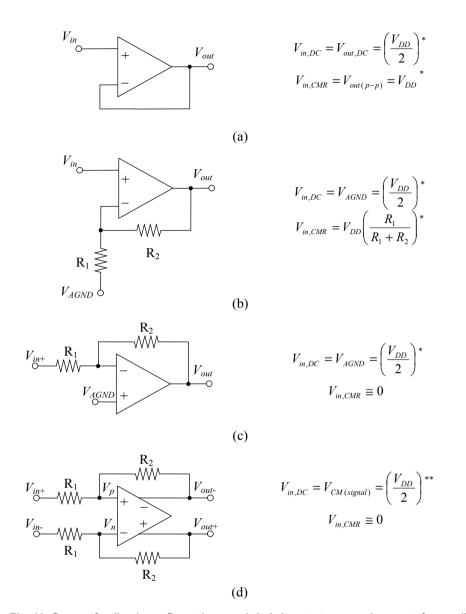

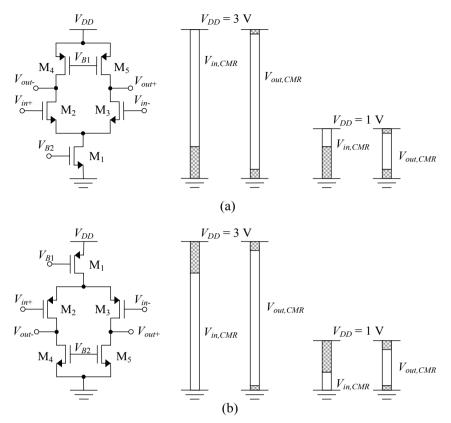

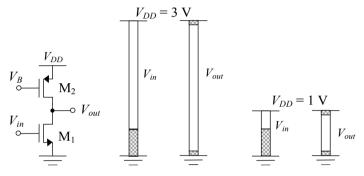

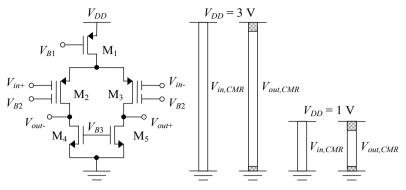

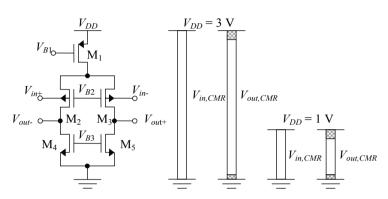

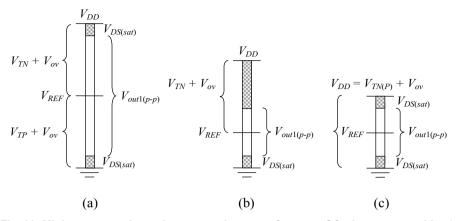

One of the most important issues caused by low supply voltage is the limited dynamic range (DR) of a circuit. The DR is the range between the maximum and the minimum signal levels. The maximum is limited by the supply voltage and the minimum by the noise floor. In order to achieve a reasonable DR and signal-to-noise ratio (SNR) for an ASP, it is desirable to keep the signal amplitude as large as possible throughout the whole circuit. Because amplifiers, filters and other active ASP circuit blocks are most often realized with opamps, the DR limitations of the analogue part is reduced to limitations of the opamps and, more specifically, their input stages. With a conventional input stage consisting of a gate-driven differential pair with a current sink (or source) this limitation manifests as an input signal common-mode range (CMR) limited close to the other rail of the supply voltages. An output stage for an opamp is easier to design for rail-to-rail operation and therefore the output voltage swing can be maximized by centering it in between the supply voltages. Depending on the application the input voltage CMR limitation can be crucial.

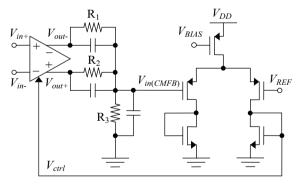

In case of an ECG amplifier, presented in Fig. 9 as a part of a QRS detector, the input signal level is very small, less than 2 mV. Therefore, the input CMR does not need to be large. However, the problem is that the input CMR of a conventional input stage with gate-driven differential pair does not reach the midsupply at low supply voltages. If the ECG amplifier is realized with a single-ended (SE) opamp (differential input and SE output) with a resistive feedback loop setting the gain, then the linear output swing and the DR of the amplifier will be limited. This is due to the fact that the feedback path from the output to the input of the amplifier sets the output DC operating point equal to the input DC operating point, which is close to the other supply rail. Therefore, the linear output voltage swing is also limited closer to the other supply rail. On the other hand, if the ECG amplifier is realized with a fully-differential (FD) opamp, then

the problem is in the design of the common-mode feedback (CMFB) circuit. Since traditional CMFB circuits have been designed using circuit structures similar to the input stages of opamps, either the resulting output swing of the FD opamp is very limited (equal to the CMR of the input stage) or the input stage of the CMFB circuit needs to be redesigned for rail-to-rail operation.

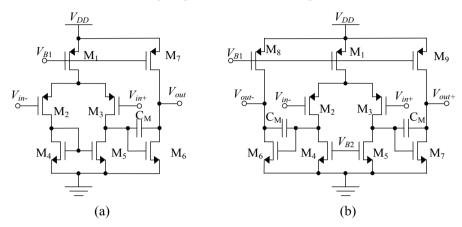

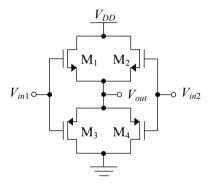

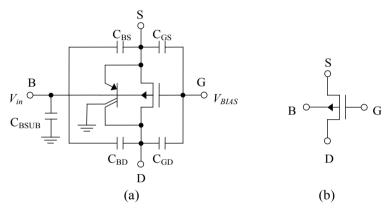

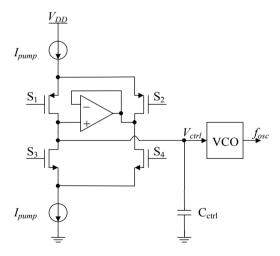

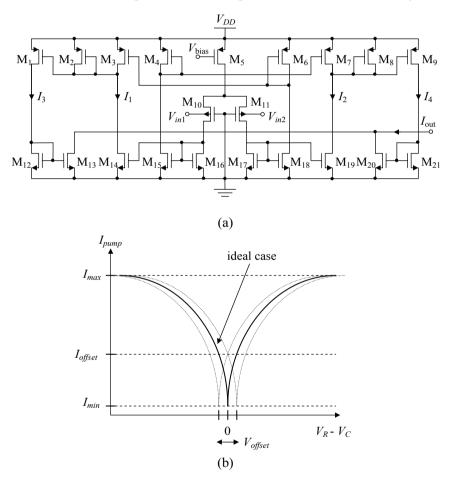

In another application, i.e. an RC oscillator developed in this work, two analogue voltages with a large dynamic range are compared with each other in order to set the output frequency of the oscillator. In this case, the input stage needs to have a rail-to-rail input voltage capability. A rail-to-rail input CMR can be achieved, for example, with a floating-gate (FG) input stage or a bulk-driven (BD) input stage, both of which are introduced in Chapters 4.1.2 and 4.1.3, respectively.

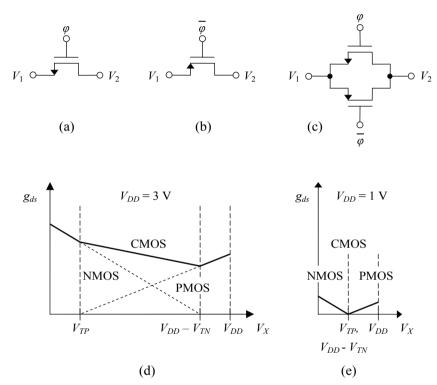

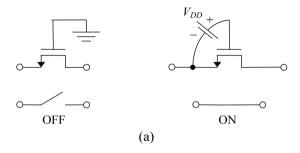

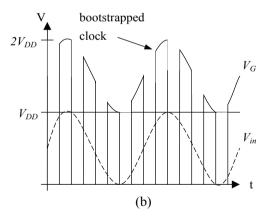

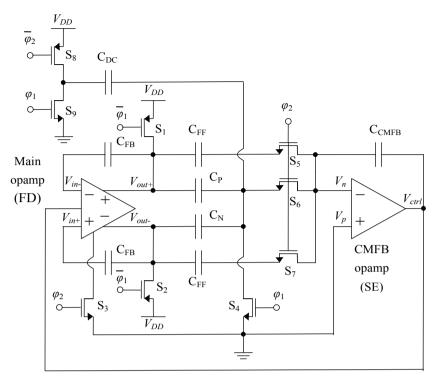

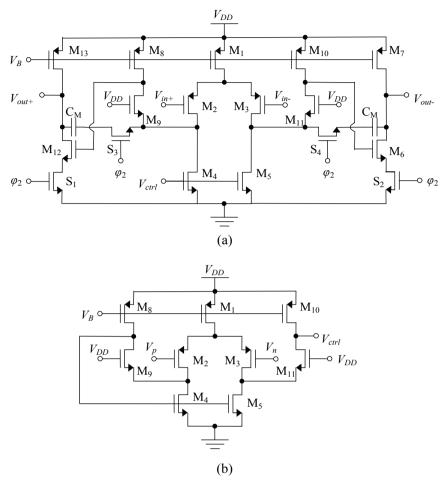

Analogue low-voltage (LV) discrete-time (DT) circuit blocks, like switchedcapacitor (SC) filters, suffer not only from the input CMR problems but also from switching problems. This is due to the reduced conductivity of a CMOS switch during its "on" state when the supply voltage is equal to or less than the sum of the threshold voltages of the switch transistors. This problem is mainly caused by series CMOS switches on the signal path. These series switches are usually located as the first switches in front of the SC circuit or at the outputs of the opamps inside the SC circuit. When the output voltage of an opamp is closer to the positive or the negative supply rail, either the PMOS or the NMOS transistor of the CMOS switch conducts the signal. When the output voltage (i.e. the signal) is around the mid-supply, neither the PMOS nor the NMOS transistor is able to conduct, a factor which will destroy the operation of the whole circuit. The series switch at the output of an opamp can be avoided by replacing both the switch and the opamp with a so-called switched-opamp circuit, which either turns the output stage or the whole opamp off during its non-active phase. Since the analogue signal processing (ASP) block for a QRS detector, presented in Fig. 9 (Chapter 2.3), is implemented using SC techniques, switching problems and their solutions will be discussed more specifically in Chapters 4.2 and 4.3.

## 4.1 Dynamic range of opamps

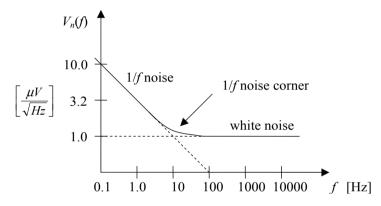

The dynamic range (DR) of an opamp is the range between the maximum and the minimum signal levels. The maximum is limited by the supply voltage and the minimum due to the noise floor. The noise performance of an opamp is an

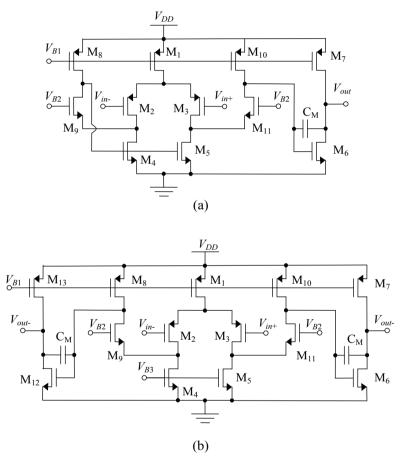

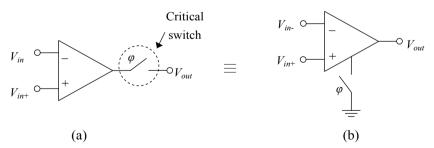

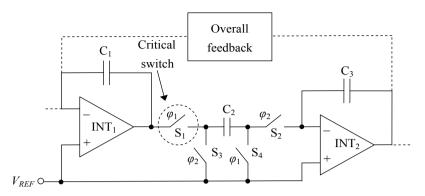

important issue especially in applications where large amplification is needed, e.g. in case of an ECG preamplifier, as presented in Fig. 9.